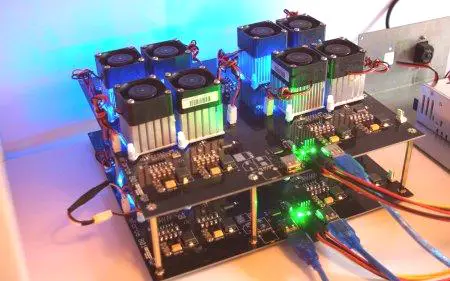

FPGA je kratica za "Field Programmable Gate Array" i predstavlja veliki niz ventila koji se mogu programirati i rekonstruirati bilo kada i bilo gdje. Mnogi korisnici još uvijek ne razumiju što je FPGA. "Ogroman skup vrata" - pojednostavljeni opis modela. Neki FPGA uređaji imaju ugrađene tvrde diskove: kontroleri memorije, komunikacijska sučelja velike brzine i PCIe krajnje točke. Unutar FPGA, postoji mnogo ventila koji se mogu slobodno spojiti. Princip rada je više ili manje sličan povezivanju pojedinih čipova logičkih elemenata. FPGA proizvode vodeće tvrtke u svijetu, Xilinx, Altera i Microsemi.

Povijest razvoja FPGA

Industrija FPGA je izrasla iz programiranih trajnih PROM memorija i PLD logičkih uređaja. Godine 1970. Philips je izumio matricu koja se može programirati na terenu. U dizajnu takve FPGA, koja se sastojala od dva plana, postignuta je specifična implementacija logičkih sklopova: funkcionalni žičani "I" ili "OR". To joj je dalo priliku da implementira funkciju u obliku zbirke proizvoda.

Altera je nastala 1983. godine, a 1984. proizvela je prvu u industriji koja može reprogramirati logički uređaj - EP300 s kvarcnim prozorima u paketu, što je omogućilo korištenje ultraljubičaste svjetiljke na matrici za uklanjanje EPROM oznake. Kako bi se prevladale poteškoće u troškovima i brzini, razvijena je programabilna logika polja, koja je uključivala samo jedan programabilni "I" uveden u fiksno "OR" vratilo. PAL iPLA, zajedno s drugim varijantama, grupirani su kao jednostavni programabilni SPLD logički uređaji. Takva FPGA, integrirana u jedan čip s predviđenim interkonekcijama za softversku vezu blokova, korištena su za zadovoljavanje rastućih tehnoloških zahtjeva. Nazivaju se integriranim PLD-ovima i razvijaju ih Altera.

Tranzistori - još jedna klasa elektroničkih uređaja zasnovana na programabilnim maskama nizova vrata. Sastoje se od nizova tranzistora koji se mogu povezati pomoću korisničkih žica. Oni su ustupili mjesto logičnim blokovima, a sada se korisnik može namjestiti na mjestu, a ne u proizvodnom laboratoriju. Ideja razvoja prvog komercijalno održivog FPGA pripada suosnivačima Xilinxa Rossa Freemana i Bernarda Wondershmitta. XC2064 je izumljen 1985. i sastoji se od 64 prilagodljivih logičkih blokova s 3 referentne tablice. On pruža moderno razumijevanje onoga što je FPGA. Krajem 1980. godine eksperiment Stevea Casselmana s kompjuterskim stvaranjem sa 600.000 reprogramiranih vrata pronašao je sponzore u Odjelu za ratne brodove mornarice SAD-a, a potom je 1992. dobio patent.

Do kraja 1990. godine došlo je do velike konkurencije u proizvodnji FPGA, a zatim je tržišni udio Xilinxa počeo opadati. Igrači kao što su Actel, Altera, Lattice, QuickLogic, Cypress, Lucent i SiliconBlue, uzeli su svoju nišu na globalnom tržištu FPGA uz Xilinx. Godine 1997. Adrian Thompson uspio je kombinirati programiranje FPGA i tehnologiju genetskog algoritma s FPGA-om, započinjući novu eru Evolvable-a. Danas je FPGA postala sasvim dovoljnapristupačan, u vezi s kojim i dalje dobivaju na popularnosti na potrošačkim tržištima. Sastoje se od skupa logičkih ćelija koje se nazivaju LUT tablice pretraživanja okružene međusobno povezanom mrežom, što omogućuje fleksibilan sustav koji može implementirati gotovo svaki digitalni algoritam.

Principi programiranja

Programiranje FPGA za početnike je proces proučavanja, planiranja, projektiranja i implementacije rješenja na FPGA. Broj i vrsta planiranja varira od programa do programa. Stvaranje dokumenta sa zahtjevima i izrada projektnog dokumenta, objašnjavajući kako će predloženo rješenje biti implementirano, može biti vrlo korisno za rješavanje potencijalnih problema.

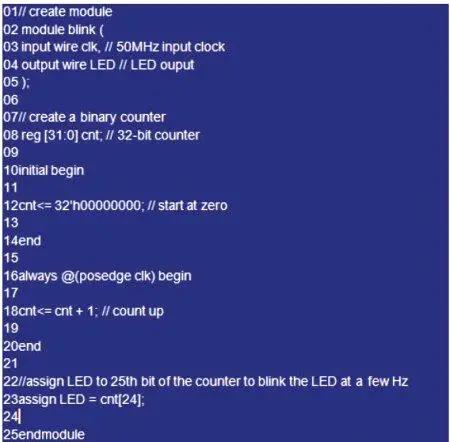

Vrijeme provedeno na izradi kvalitetnog projektnog dokumenta uštedjet će ga u budućnosti na prepravci, otklanjanju pogrešaka i ispravljanju pogrešaka. Implementacija FPGA programskog rješenja uključuje projektiranje projekta koristeći jednu od metoda provedbe projekta. Među njima su sheme ili HDL kodovi, kao što su Verilog ili VHDL. FPGA može programirati izvornu datoteku FPGA fizičkom uređaju pomoću alata FTP programiranja. Uvođenje dizajna uz korištenje shema više se ne koristi u industriji. Sinteza i programiranje gotovo su se u potpunosti pobrinuli za alate dobavljača, kao što su konfiguracijski alati ISE i Vivado i Numato Lab.

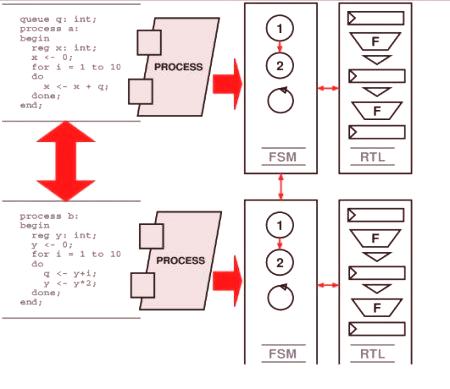

Stopa RTL prijenosnog registra

RTL označava brzinu prijenosa registra. Programer također može naići na uvjete Register Transfer Logic ili Register Transfer Language, svi oni značeisto u dizajnu opreme. RTL je apstrakcija više razine za digitalni dizajn hardvera, koja se nalazi negdje između strogo ponašanja simulacije na jednom kraju i čisto strukturne na razini gateway - s druge strane. Simulacija ulaza znači opis hardvera s upotrebom osnovnih ventila, što je prilično oslabljujuće. RTL se može promatrati kao analog izraza "pseudo-kod" koji se koristi u FPGA programskom okviru. Možete opisati dizajn hardvera kao niz koraka ili tokova podataka iz jednog skupa registara u sljedeći u svakom ciklusu takta. RTL se također naziva i dizajn "stream podataka". Čim je RTL projekt spreman, lakše je pretvoriti u pravi HDL kod pomoću jezika kao što su Verilog, VHDL, SystemVerilog ili bilo koji drugi hardverski jezik. FPGA je mnogo više od skupa vrata. Iako je moguće izgraditi logičke sheme bilo koje složenosti, organizirati i povezati logičke elemente. To je način da se izrazi logika u jednostavnom formatu, koji se na kraju može pretvoriti u niz elemenata. Dvije popularne metode za to su: uvođenje sheme i opis jezika HDL opreme. Prije nego što je postao široko korišten, inženjeri su dizajnirali sve kroz sheme. Bili su vrlo jednostavni za male projekte, ali bolno neupravljani - za velike. Zamislite kako Intelovi inženjeri izvlače krug za Pentium, s milijunima pristupnika! To je neprihvatljivo teško.

Verilog je opis HDL hardvera za koji možete koristitidigitalni krugovi u običnom tekstu. Učenje Veriloga nije tako teško ako korisnik ima iskustvo u programiranju. VHDL je još jedan popularni HDL, široko korišten u industriji. Verilog i VHDL-ovi imaju manje-više isto priznanje na tržištu, ali korisnici obično biraju Verilog jer ga je lako naučiti i ima sintaktičku sličnost sa C jezikom.

Tehnologije programiranja

FPGA-i se mogu smatrati gradivnim blokovima koji vam omogućuju pravilno postavljanje opreme. To je poseban oblik PLD-a s većom gustoćom i proširenom funkcionalnošću u kraćem vremenskom okviru pomoću CAD-a. FPGA su dostupne u različitim verzijama na temelju korištene tehnologije programiranja. Mogu se programirati pomoću:

Antifuse tehnologije. Programiranje temeljeno na tehnologiji Flash uređaja iz Actela. FPGA se može reprogramirati nekoliko tisuća puta, što traje nekoliko minuta u polju za reprogramiranje i ima trajnu memoriju.FPGA na temelju SRAM-a, koji nudi neograničeno reprogramiranje i vrlo brzu rekonfiguraciju ili djelomičnu rekonfiguraciju tijekom samog rada s malim brojem dodatnih krugova. Većina tih tvrtki, kao što su Altera, Actel, Atmel i Xilinx, proizvode ove uređaje.

Konfigurirani logički blokovi

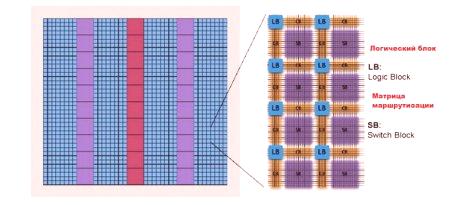

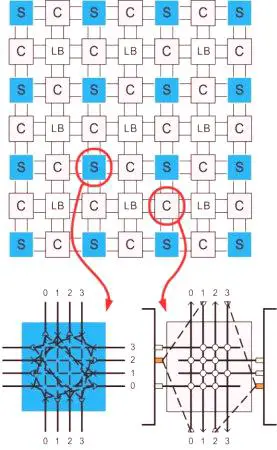

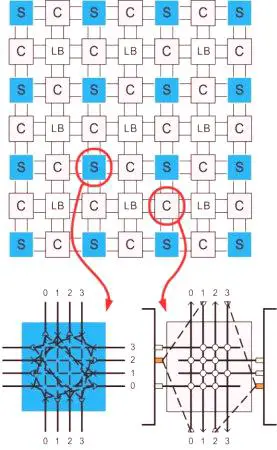

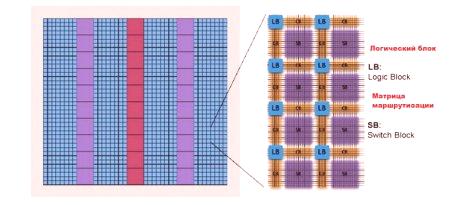

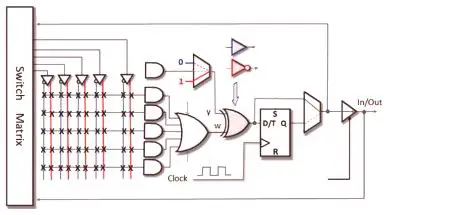

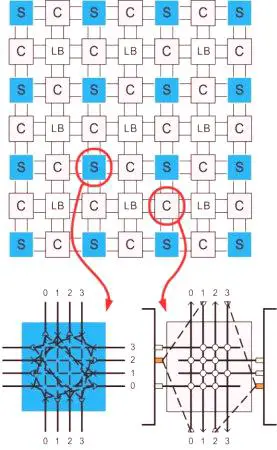

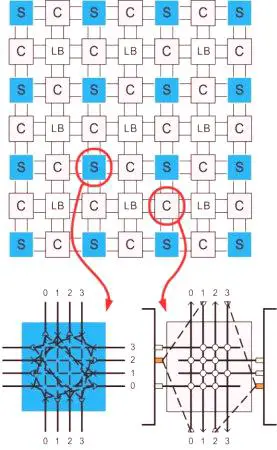

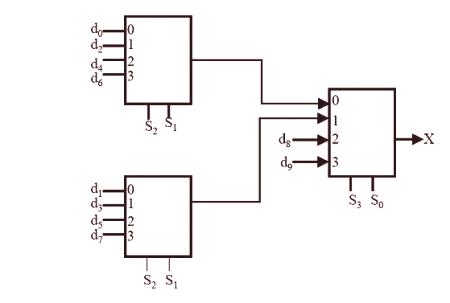

Bez obzira na različite proizvođače i nekoliko različitih arhitektura i skupova funkcija, većina FPGA ima zajednički pristup. Glavni sastavni blokovi bilo kojeg FPGA su fleksibilni programabilni "logički blok" (CLB), okružen programabilnim "blokovima"I /O "s hijerarhijom kanala za usmjeravanje koji povezuju različite blokove na ploči.

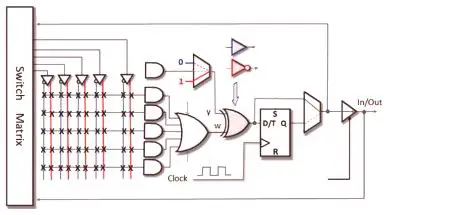

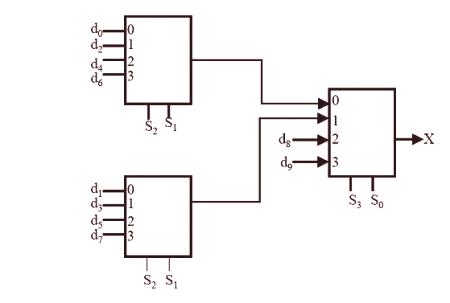

Osim toga, mogu se sastojati od DLL-ova za dodjelu i kontrolu sati i RAM-a odabranog bloka s glavnim građevnim blokom logičke ćelije. Potonje se sastoji od generatora ulaznih funkcija, logike prijenosa i pohrane elemenata. Generatori se implementiraju u obliku referentnih tablica i ovise o ulazu. Na primjer, Xilinx Spartan II ima 4 ulaza LUTs, pružajući svaki 16X1-bitni sinkroni RAM pomoću multipleksera kao pomak registara za snimanje podataka u batch načinu rada. Elementi za pohranu su osjetljivi na rubove okidača ili na razinu zasuna. Fragmentacija FPGA:

Aritmetička logika uključuje XOR pristupnik za rad s punim sabiračem i dodjeljivanje logičkih prijenosnih linija. Blok I /O i matrica usmjeravanja. Ovaj uređaj ima ulaze i izlaze koji podržavaju širok raspon standarda i sučelja za signalizaciju.Donji I /O blok je prikazan ispod. Međuspremnik ispod ulaznih i izlaznih putova šalje signale internoj logici i konačnoj platformi izravno ili kroz okidač. Konfigurirani su u skladu s različitim podržanim standardima alarma, koje korisnik može definirati i instalirati izvana.

Matrica usmjeravanja

Na bilo kojoj montažnoj traci, spor segment određuje ukupne performanse. Algoritmi usmjeravanja koriste se za razvoj najučinkovitijih načinaosigurava optimalne performanse. Usmjeravanje se izvodi na različitim razinama kao što je lokalno, opće usmjeravanje između različitih CLB-ova, I /O usmjeravanje između blokova i CLB-a, namjensko usmjeravanje za određene klase signala kako bi se povećala produktivnost i Global Routing za mjerenje takta i drugih signala s vrlo velikim grananjem. , FPGA obitelji također imaju veliku blok strukturu RAM-a za dopunu LUT RAM-a, čija veličina varira za različite FPGA uređaje.

Dizajn FPGA u osnovi uključuje isti pristup kao i svaki VLSI sustav, čije su glavne faze projektiranje, simulacija ponašanja, sinteza, simulacija nakon sinteze, emitiranje, mapiranje i usmjeravanje, kao i daljnja analiza kao što je simulacija sinkronizacije i statička sinkronizacijska analiza. Na računalu dizajn izgleda uredno i popločan, ali zapravo postoji nesavršen položaj i usmjeravanje, što dovodi do smanjenja performansi. Uvijek možete koristiti više tranzistora za povećanje FPGA performansi. Područje servisa je visoko. Instaliranje više tranzistora znači da su moguće velike izvedbe. Propuštanje je ozbiljan problem za FPGA i istovremeno je od interesa. Korištenje asinkrone arhitekture FPGA pokazuje bolje rezultate u kombinaciji s transportnom tehnologijom, što smanjuje globalne ulaze i poboljšava propusnost.

Pitanja kvalitete i vrata

Sigurnost sustava je uvijek bilaglavni problem, jer kod bi trebao biti otvoren svaki put kada se učita u FPGA. Ta fleksibilnost čini FPGA potencijalnom prijetnjom zlonamjernim modifikacijama u proizvodnom procesu, tako da je šifriranje tokova bitstream-a došlo na njegovu pomoć na vrijeme. Često se neiskusni dizajneri i korisnici suočavaju s dilemom koliko je FPGA moćan za njihov razvoj. Proizvođači često navode metrike, na primjer, "broj vrata". Na primjer, Xilinx FPGA programiranje koristi 3 metrike za mjerenje FPGA volumena, maksimalnih logičkih elemenata, maksimalnih bitova memorije i tipičnog raspona pristupnika. Premda su dosljedni, migracija između modela je pomalo pojednostavljena, ali rijetko nudi precizne usporedbe među različitim dobavljačima zbog raznolikosti u arhitekturi i zbog razlika u performansama. Najbolji pokazatelj je usporedba vrste i količine pruženih logičkih resursa. Osim toga, programer mora u potpunosti razumjeti što se točno zahtijeva od uređaja, budući da se proizvođači mogu pohvaliti značajkama koje će biti najmanje važne za rad. Primjerice, Altera Stratix II EP2S180 ima oko 186576 LUT-ova s 4 ulaza, a Xilinx Virtex-4 XC4VLX200 sadrži 178176. Međutim, ako projektiranje zahtijeva samo 177 tisuća LUT-ova, to će biti dovoljno.

Ako je RAM željena metrika za dizajnera, onda ni 6 Mbit Xilinx XC4VLX200 niti 9 Mbit Altera EP2S180 neće biti bolji od manje reklamiranog, starijeg modela XC4VFX140 sa 99 Mbit.

Programski jezici i softver

Programiranje FPGA Altera za početnike počinje s izborom jezika. Opcija C, C ++ iliSustav C omogućuje korištenje mogućnosti najvećih uređaja i istovremeno postiže sličnost realistične razvojne grafike. Mogućnost korištenja C-baziranog dizajna za FPGA osigurava HLS (sinteza na visokoj razini), koja je već godinama na pomolu s alatom kao što je Handle-C. nedavno je postala stvarnost zahvaljujući činjenici da veliki dobavljači Altera i Xilinx nude HLS u svojim Spectra-Q i Vivado HLx setovima alata. Dostupan je niz drugih programskih implementacija Altera FPGA programa za početnike temeljene na C, kao što je OpenCL, koji je dizajniran za programere koji žele povećati produktivnost FPGA bez dubokog razumijevanja FPGA dizajna. Kao i kod HDL-a, HLS ima ograničenja pri korištenju FPGA pristupa programiranju C, kao i kod tradicionalnih HDL-ova, programeri moraju raditi s podskupom jezika. Na primjer, teško je sintetizirati i implementirati sistemske pozive, jer morate biti sigurni da je sve ograničeno i da ima fiksnu veličinu. U HLS-u je lijepo što možete dizajnirati vlastite algoritme s pomičnim zarezom i postoji alat za konverziju HLS-a s pomičnim zarezom u fiksni. Programiranje FPGA s Xilinxom uopće nije teško. Možete ga dobiti kupnjom Xilinx proizvoda besplatno ili po modelu specifičnom za cijenu. Videozapisu možete pristupiti na web-lokaciji profila, što jasno pokazuje postupak korištenja. Od svih tvrtki koje se mogu odabrati prilikom traženja programabilnih polja, Xilinx je definitivno najbolje od svega. Oni su kreatori ovog proizvoda i višemnogo godina učinilo ga je poboljšanjem. Firmware je postao moćniji nego ikada prije.

Faze projektiranja

Programiranje FPGA-a može se provoditi online, budući da je platforma dobro predstavljena na internetu. Prilikom postavljanja FPGA, prvi korak je osmisliti sklop za koji je potrebno znanje digitalne elektronike. Za razliku od programiranja, mnogo je teže započeti s rezanjem koda ako arhitektura programa nije jasna. Čim postane jasno da je potrebno implementirati, počnite opisivati shemu, koristeći jedan od jezika: Verilog ili VHDL. Činjenica da se paradigma mijenja je da se oni ne nazivaju programskim jezicima FPGA-a, ali su jezici opisa. Zbog složenosti testiranja digitalnih sklopova, banke obično u ovoj fazi koriste testove koji simuliraju ponašanje opreme. Ovaj tip alata omogućuje vam da vidite status signala u bilo kojem trenutku i da provjerite ima li prijelaza s željenim rezultatima.

Treći stupanj poznat kao sinteza sheme je jedan od ključnih. Odabire korištene elemente i njihove međusobne veze u skladu s datotekama opisa. U ovoj fazi trebate alate koji u većini slučajeva pojednostavljuju i automatiziraju zadatke.

Hardver i ispravljanje pogrešaka

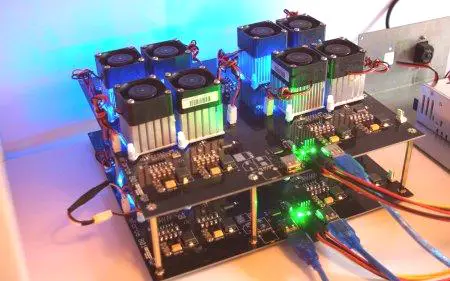

Intel Quartus Prime Software Suite Lite Edition - softver za projektiranje FPGA. Savršen je za početnike jer ga možete besplatno preuzeti i ne trebate licencnu datoteku. Softver možete preuzeti na web-mjestu proizvođača. Njihova veličina (nekoliko gigabajta)Preuzimanje i instaliranje može potrajati dugo. Da biste smanjili vrijeme i potreban prostor na disku, preporučujemo da preuzmete samo one stavke koje su potrebne za prilagođene zadatke. Kada se zatraži, datoteke za preuzimanje, uklonite kvačicu "Select All" i odaberite samo Quartus Prime i podršku za Cyclone V uređaj. Algoritam za projekt:

Otvorite novi čarobnjak projekta. Odaberite Sljedeće & gt; Katalog & gt; & gt; Imenujte objekt najviše razine.

Odaberite direktorij za postavljanje projekta, na primjer, "Blink" i smjestite ga u mapu intelFPGA_lite, ali možete je postaviti bilo gdje i kliknuti "Next". Kada se od vas zatraži da kreirate direktorij, odaberite "Da". Odaberite "Isprazni projekt" i kliknite "Dalje". Dodavanje datoteka i "Dalje". Podesite obitelj, uređaj i ploču odabirom sljedećeg: obitelj - Ciklon V, uređaj - Cyclone V SE, baza, naziv uređaja: 5CSEBA6U2317. Da biste odabrali određeni uređaj, trebate kliknuti strelice gore /dolje da biste vidjeli popis podržanih uređaja dok se ne pojavi 5CSEBA6U2317. Korisnik će možda morati proširiti polje "Ime" kako bi vidio puno ime uređaja, kliknite "Dalje". Prilikom postavljanja EDA alata koriste se standardni alati, tako da se neće vršiti promjene, kliknite "Next" i "Done". Pojavljuje se zaslon sažetka. Stvorite HDL datoteku s uvođenjem Veriloga kao HDL. Idite na karticu Datoteka (glavni prozor) i odaberite Novo. Odaberite Verilog HDL datoteku i kliknite OK. Odaberite Datoteka & gt; "Spremi kao".Odaberite naziv datoteke. Ovo je ime datoteke najviše razine i mora odgovarati nazivu projekta. Kliknite "Spremi". Stvorite Verilog modul. Kopirajte i zalijepite Verilog kod dolje u prozor blink.v, a zatim spremite datoteku koda. Desnom tipkom miša kliknite Analiza i sinteza, a zatim kliknite Start za provjeru Verilogove sintakse i verifikacije sinteze.Ako je proces uspješno završen, zajedno s analizom i sintezom, prikazuje se zelena kvačica. Ako se pojavi pogreška, provjerite sintaksu i provjerite da li se točno poklapa s gore navedenim blokom koda. Svi iskusni programeri znaju da složeni programi, čak i potprogrami, ne rade ispravno od prvog puta. Sposobnost apstrakcije osobe koja se temelji na iskustvu omogućuje mu da pronađe rješenje bez brige o najmanjim detaljima. No, rigorozna istina je da fizički sustav u koji je program ugrađen zahtijeva da se svaki mali detalj uzme u obzir prije nego što sve počne raditi. Razvojem softverskih alata za razvoj FPGA, uglavnom od tradicionalnih dobavljača kao i neovisnih pružatelja alata: Synplicity, FPGA - postaje sve popularniji iz dana u dan. Sada FPGA je počeo da uključuje specijalizirani hardver pružiti kupcu potrebne značajke, smanjujući troškove za proizvođače. Tako se u budućnosti može pojaviti konkurencija između tvrdih i jeftinih sustava s fleksibilnim kernelima. Očekuje se da će se u bliskoj budućnosti troškovi smanjiti još više zbog popularnosti FPGApovremeno će se povećavati. Proizvođači su počeli eksperimentirati s konceptom ugradnje FPGA-ova u integrirane sklopove kako bi stvorili hibridni uređaj. Fokus je još uvijek na usmjeravanju interkonekcija, a manje promjene se promatraju u CLB arhitekturi. Budući da FPGA-i nastavljaju uključivati procesore, nova generacija zahtijeva ne samo znanje o hardveru digitalnog dizajna, već i iskustvo programera u procesu jednokratnog programiranja FPGA. Općenito, očekuje se da će FPGA oduzeti tržišni udio u ASIC uređajima i postati dominantna tehnologija koja obuhvaća mnoge aplikacije iz različitih područja.